Fall 2016

# Power Electronics

EE 3305 LECTURE NOTES

Dr. M. Aba-Khaizaran

Electrical and Computer Engineering Department-BZU

# Part VI: DC-to-AC Converters (Power Electronic Inverters)

#### Introduction:

Inverters are power electronic circuits designed to convert a DC voltage (or current) into an AC voltage (or current). The output of these inverters consists of a fundamental component of voltage or current, plus other (undesirable) components at higher frequencies called harmonics.

## Types of Inverters According to Type of Input Source

The Inverters can be classified according to the characteristic of the input source to:

- Voltage Source Inverters

- Current Source Inverters

# Main Types of Inverters:

#### Voltage Source Inverters (VSIs)

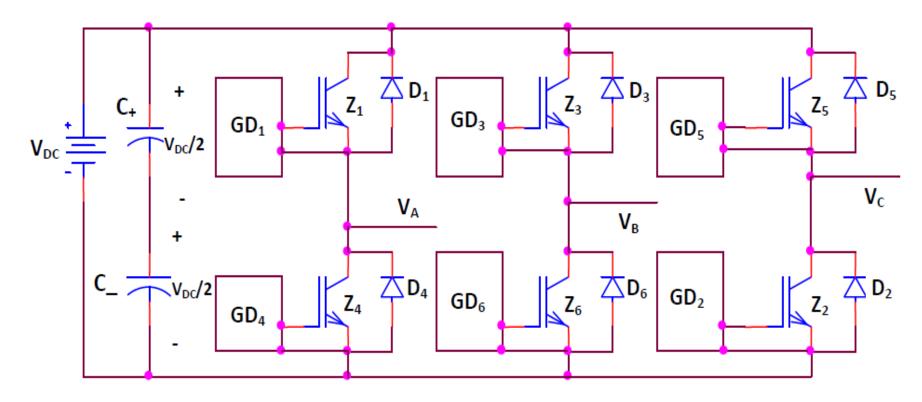

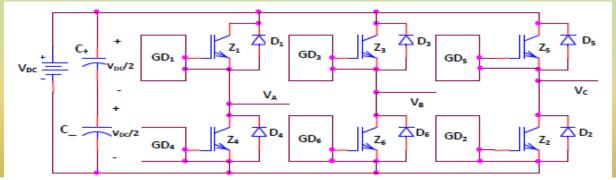

The input to the inverter is assumed to be a constant DC voltage source; it could be a rectified AC supply with a filter. A typical three-phase Voltage Source Inverter (VSI) is shown in the Figure below.

The switches in a VSI have the ability to conduct current in both directions (upwards and downwards).

- The switches in a VSI have the ability to conduct current in both directions (upwards and downwards).

- Therefore, each switch has an anti-parallel diode; either the body diode or an external fast reverse recovery diode.

- A Dead time (Underlap period) between switches in the same leg, where both switches are off, should elapse before turning on the off-switch. Typically, the Dead time ranges from 1μs to 5μs, depending on the switching speed of the switches used, the circuit's topology and layout, and power level.

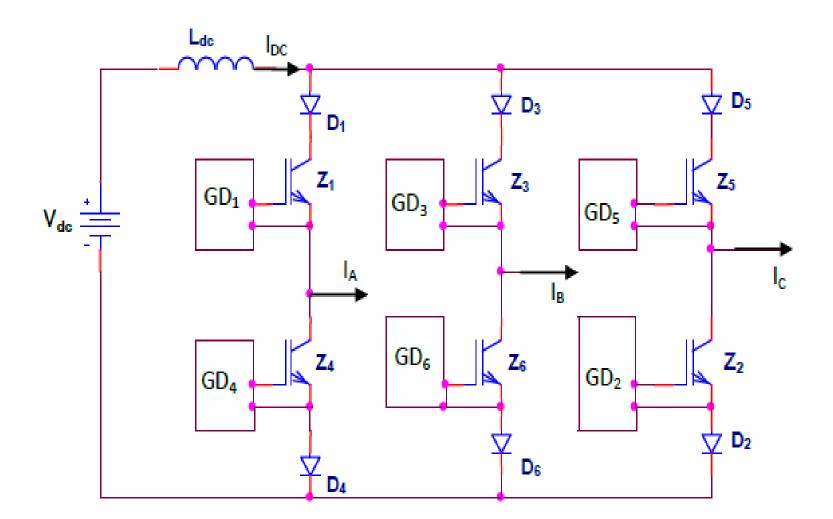

# ) Current Source Inverters (CSIs)

The input to the inverter is assumed to be a constant DC current source. A voltage source in series with a large inductor represents a current source. A typical three-phase Current Source Inverter (CSIs) is shown in the Figure below.

- The switches in a CSI must have the ability to support (block) voltage of both polarities.

- Therefore, each switch has a reverse blocking capability; if switches with only forward blocking capabilities are used, a diode is connected in series with each switch to attain reverse blocking capability.

- An Overlap time (period) between switches in the same level of the inverter (upper or lower), where both switches are on, should elapse before turning off the conducting switch. Typically, the Overlap time ranges from 1μs to 5μs, depending on the switching speed of the switches used, circuit's topology and layout, and the power level.

# Applications:

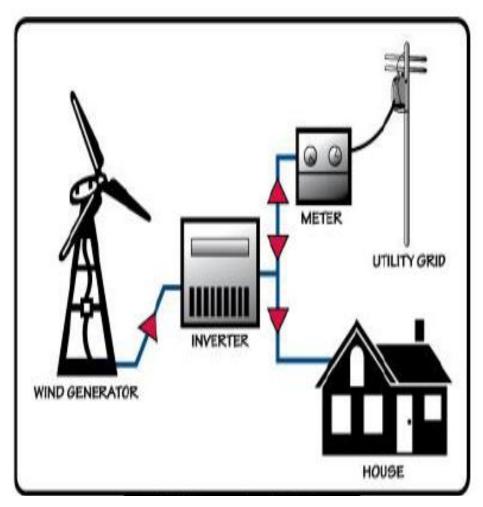

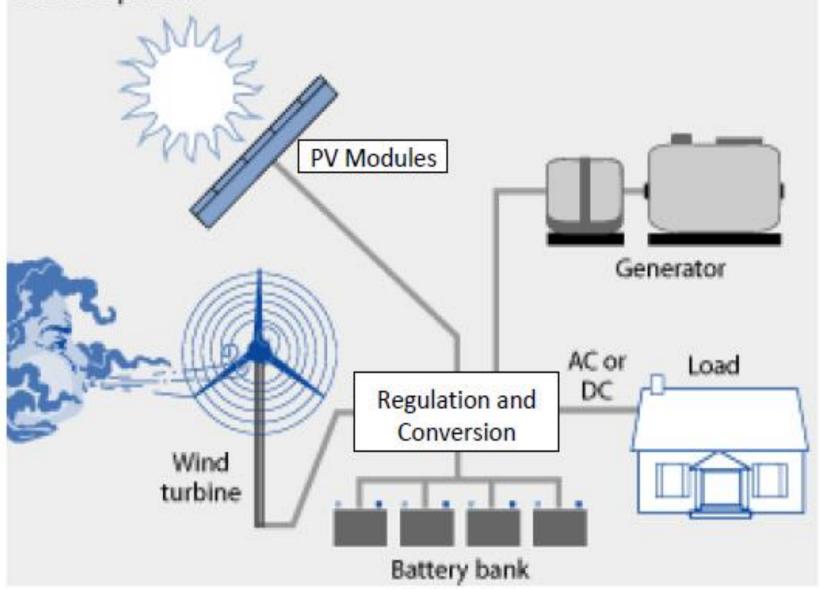

The main applications of inverters are AC Motor Drives, Uninterruptable Power Supplies (UPSs), and Interconnection of PhotoVoltaic (PV) and Wind electric system with the Utility Grid. Inverters are essential components in renewable energy systems.

# PhotoVoltaic System

**Grid Connected Wind System**

# Hybrid Power Systems

Combine multiple sources to deliver non-intermittent electric power

## **Switching Schemes**

Since the output of these inverters follows the control voltage of gates/bases of the controllable switches, various switching schemes can be employed to obtain an AC output of the various types of inverters. These schemes vary in their complexity, quality of output, switching losses, harmonic content and magnitude of AC gain. Some of these:

#### 1. Square Wave Strategy

The gate/base control signals have a square wave shape with a duty cycle of half the period. This method is simple, but the harmonic content is high! This method will be studied in details later.

#### 2. Sinusoidal Pulse Width Modulation (SPWM) Method

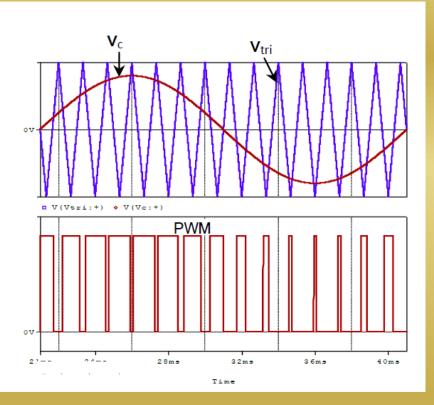

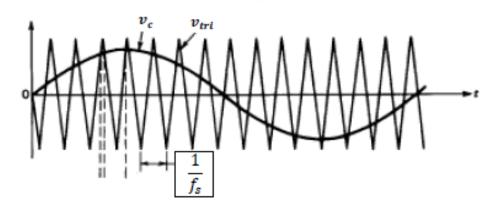

Since the desired outputs are sinusoidal, the control signal(s) has(ve) a sinusoidal shape. Therefore, the outputs are more closely sinusoidal with less harmonic content.

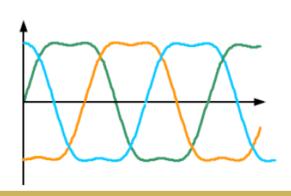

The control voltage is compared with a triangular voltage to produce the gate signals of the controllable switches, as shown in the Figure next.

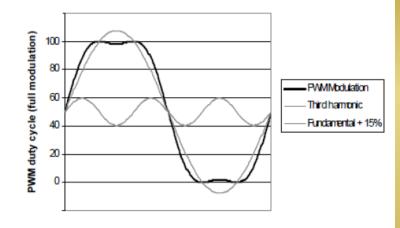

#### 3. Sinusoidal Pulse Width Modulation with Third Harmonic Injection Method

This method is applicable to three-phase inverters. Each control signal, which is sinusoidal, has an added Third Harmonic signal to increase the AC gain compared to that of SPWM method. The frequency of the Third Harmonic signal is three times that of the fundamental frequency, but its magnitude is fractions of the magnitude of the sinusoidal signal.

The per-unit modified control voltage (Third Harmonic Modulation Equation) is:

$$v_c(t) = \frac{2}{\sqrt{3}}\sin \omega t + \frac{1}{3\sqrt{3}}\sin 3\omega t$$

$$\Rightarrow v_c(t) = 1.155 \sin \omega t + 0.1925 \sin 3\omega t$$

The amplitude of the Modified reference control voltage cannot exceed 100%, but its fundamental component can. This produces a fundamental output voltage higher than that is obtained from SPWM by about 15.5%. Consequently, this method provides a better utilization of the DC supply.

Three-Phase Modified Sinusoidal Voltages with Third Harmonic Injection are in the Figure next.

#### 4. Harmonic Elimination Method

The outputs are shaped with a number of notches removed at specified angles calculated by a microprocessor or a microcontroller in order to eliminate particular harmonics.

#### 5. Space Vector Modulation (SVM) Scheme

The three phase outputs are formed according to switching states sequence of the inverter switches. This method has a higher AC Gain compared with SPWM, less switching losses, and it is more feasible for digital implementation. This scheme will be studied in more details later in this course.

The AC Gain ( $G_{AC}$ ) is defined as the maximum value of the fundamental component of the line-to-line voltage to the amplitude of the unfiltered pulses compromising the same component (the DC value).

For a three-phase Voltage Source Inverter, the AC Gain is defined as:

$$G_{AC} = \frac{\widehat{V}_{LL1}}{V_{DC}}\Big|_{M=1}$$

# 1) Square Wave Operation of Voltage Source Inverters

# 1.1) Single Phase Voltage Source Inverter (Full Bridge as a DC-to-AC Converter)

## A. Single Phase VSI in Square Wave Mode

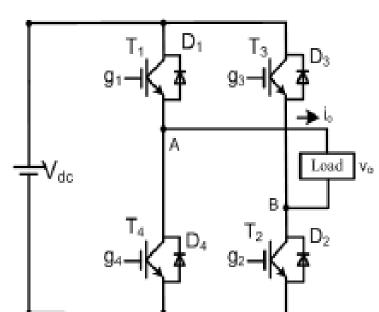

The Full Bridge can be operated in a Square Wave Mode to function as a single-phase Voltage Source Inverter producing an AC voltage at the output. The Figure below shows the circuit diagram of a single-phase VSI implementing IGBTs as switches.

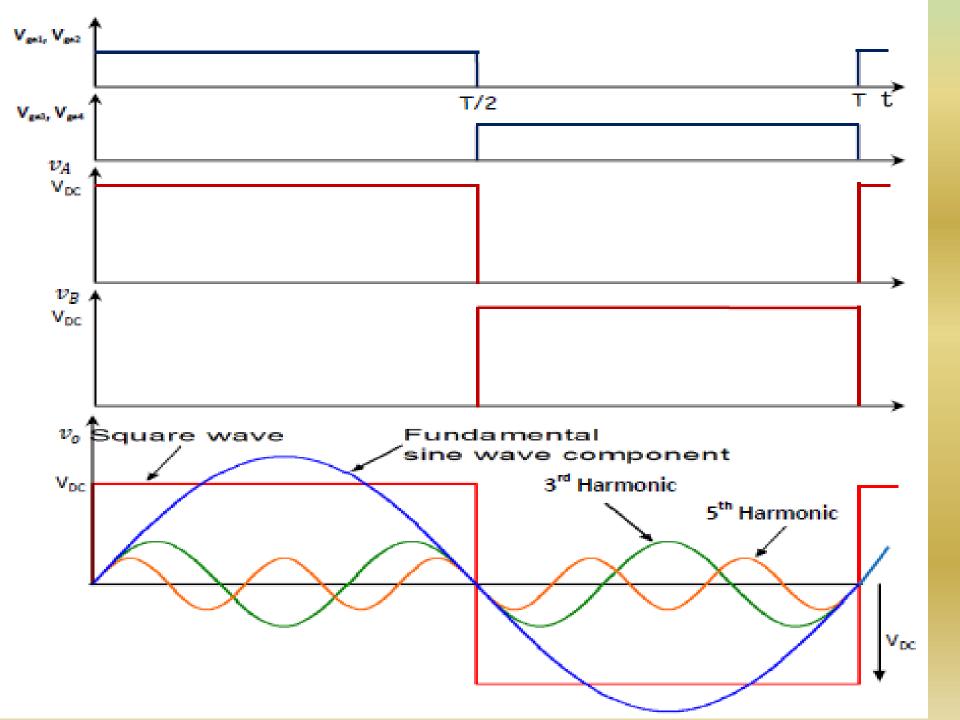

Each of the inverter switches is 'on' for one half of a cycle  $(180^{\circ})$  of the desired output frequency  $(f_1)$ .

The output square wave consists of an infinite number of sinusoidal voltages; a fundamental component and other high frequency components (harmonics).

- The frequency at the output ranges from few Hz up to MHz.

- The frequency can be adjusted by varying the frequency  $(f_1 = \frac{1}{r})$  of the controlling signals.

- The Figure next page shows the gate-emitter voltages of the IGBTs, the output voltages of the mid points of inverter legs with respect to the negative terminal of the supply, and the output voltage of a single-phase VSI with a Square Wave Mode.

- The Frequency Analysis gives the amplitude of the output at the fundamental frequency  $f_1\left(=\frac{1}{T}\right)$  as:

$$\hat{V}_{o1} = \frac{4}{\pi} V_{DC} = 1.273 \ V_{DC}$$

The amplitude of the AC output can be controlled by varying the DC input voltage, which could, for example, be derived from a Boost converter.

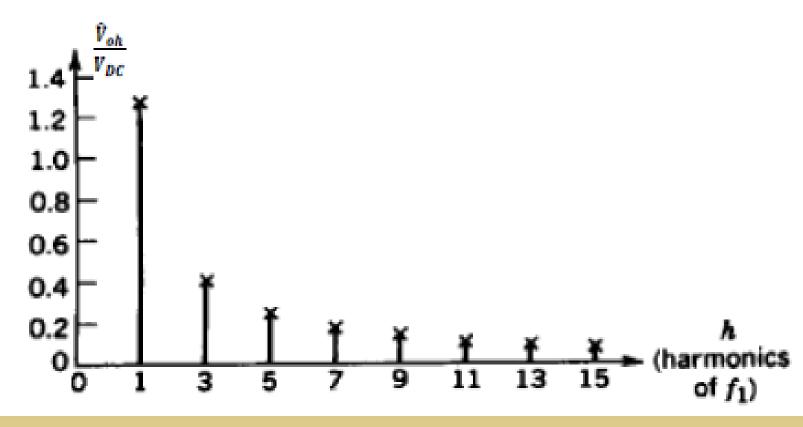

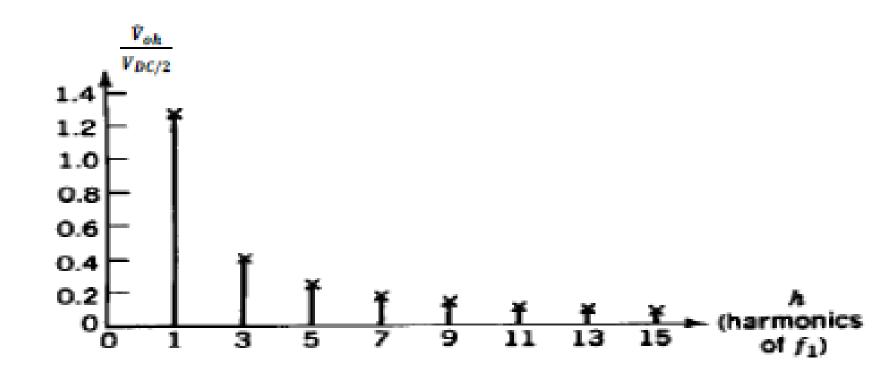

The harmonic components of the output are:

$$\hat{V}_{oh} = \frac{\hat{V}_{o1}}{h} = \frac{4}{h\pi} V_{DC}$$

where h takes odd values only!

Thus, the Frequency Spectrum of the output in a Square Wave Mode is shown in the Figure below.

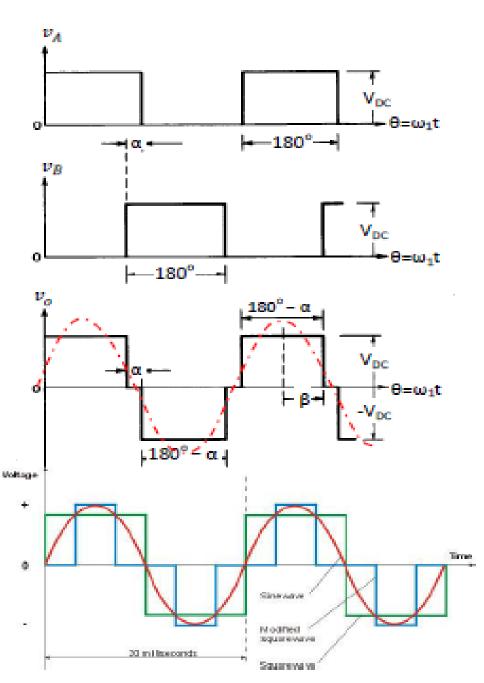

#### B. Single Phase VSI Voltage Cancellation Method for Square Wave Mode

The AC output voltage and its harmonic content can be varied by switching the legs of the inverter independently. The duty cycle of Leg A  $(k_A)$  is made equal to the duty cycle of Leg B  $(k_B)$  and equals 0.5. But, the switching is phase shifted with an angle (delay),  $\alpha$ , between the two legs, so that the voltage is cancelled at the output for particular angles. Hence, it is called Voltage Cancellation Method.

The amplitude of the fundamental component at the output and its harmonics are again obtained by Fourier Analysis as:

$$\hat{V}_{oh} = \frac{2}{\pi} \int_{-\pi}^{\frac{\pi}{2}} v_o \cos (h\omega t) d\omega t$$

$$\hat{V}_{oh} = \frac{2}{\pi} \int_{-\beta}^{\beta} V_{DC} \cos (h\omega t) d\omega t$$

Evaluating the integral and simplifying yields:

$$\hat{V}_{oh} = \frac{4}{h\pi} V_{DC} \sin{(h\beta)}$$

where  $\beta = 90 - \frac{\alpha}{2}$  and h is also an odd

integer!

Setting  $\alpha = 60^{\circ}$  removes the third harmonic component and multiples of it (no Triplen harmonics).

1.0

0.8

0.6

0.4

0.2

Fundamental

- The minimum Total Harmonic Distortion (THD) is achieved with selecting  $\alpha$  to be slightly less than  $60^{\circ}$  ( $\sim55^{\circ}$ ); as illustrated in the Figure next, noting that the Y-axis is normalized.

- Remember that the Total Harmonic Distortion (THD) is the ratio of the harmonic contents to the value of the fundamental component, and is given by:

$$THD = \frac{1}{\hat{V}_{o,1}} \sqrt{\sum_{h=3}^{\infty} \hat{V}_{o,h}^2} X100\%$$

Filtering is required if the load cannot tolerate the harmonic currents.

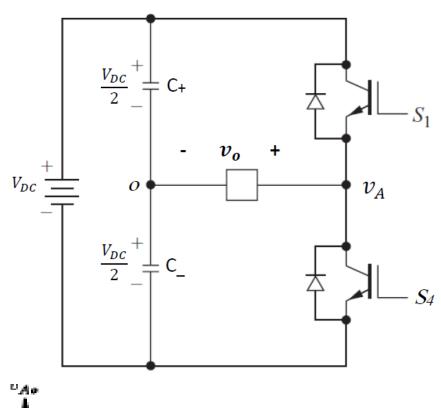

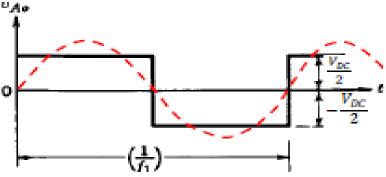

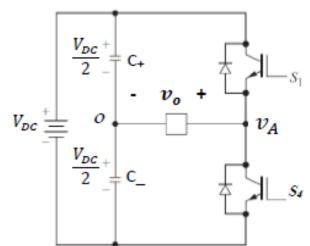

#### 1.2) Half Bridge (an Inverter Leg)

- ▶ One leg of the Full Bridge can be replaced, for AC operation only, by two large and equal capacitances.

- The inverter leg configuration is shown in the Figure next.

- The capacitances can be very expensive unless the output frequency is very high.

- Regardless of the switches' states, the current divides equally between the two capacitors; C<sub>+</sub> and C\_.

- The midpoint between the two capacitors stays at the same potential;  $\frac{V_{BC}}{2}$ .

- The voltage across the load is half the value obtained from the single-phase VSI (Full Bridge) and is given by:

$$\hat{V}_{o1} = \frac{4}{\pi} \frac{V_{DC}}{2} = 0.637 V_{DC}$$

and the harmonics are:

$$\hat{V}_{oh} = \frac{4}{h\pi} \frac{V_{DC}}{2} = \frac{1}{h} 0.637 V_{DC}$$

Also, h is an odd integer.

The Frequency Spectrum of the output is illustrated in the Figure below.

# 1.3) Three-Phase Voltage Source Inverters in Square Wave Mode

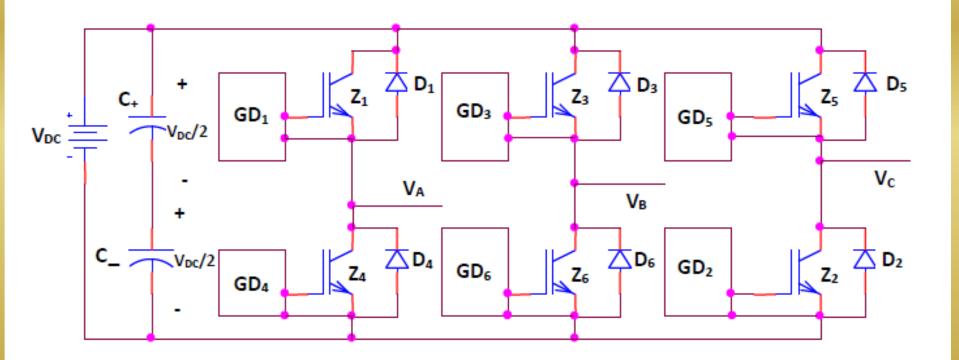

Three Half Bridge Legs can be connected in parallel, as illustrated in the Figure below, to generate three-phase output voltages.

- The numbering sequence is the same as the conventional numbering sequence.

- Each IGBT has an anti-parallel diode.

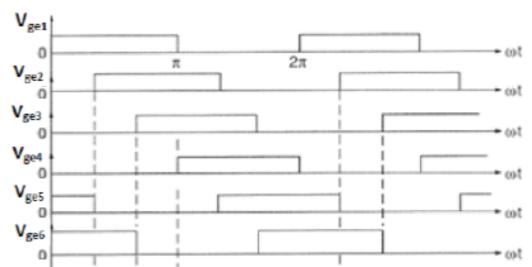

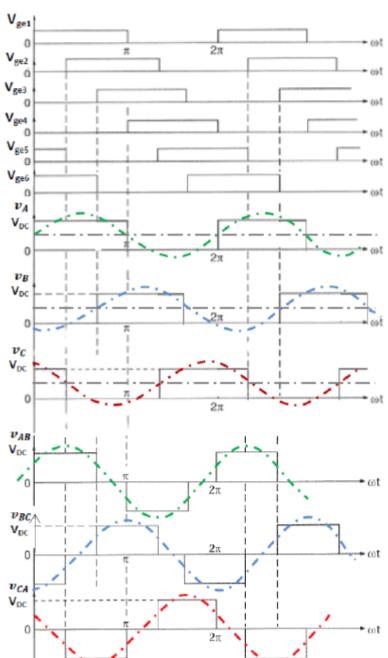

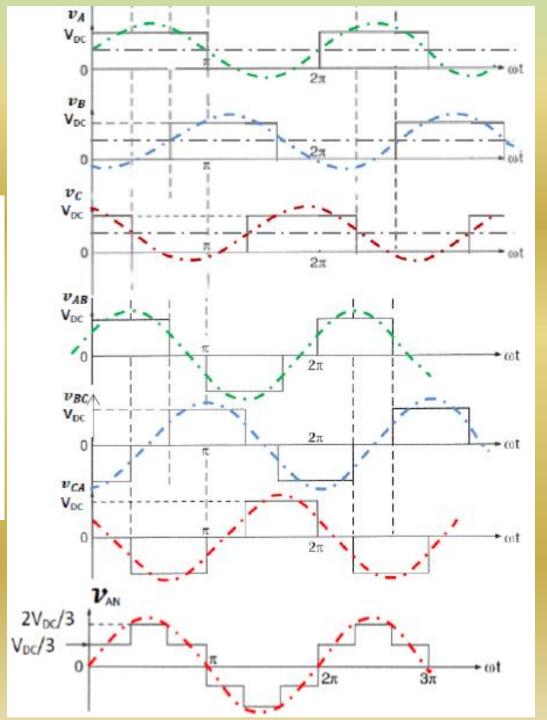

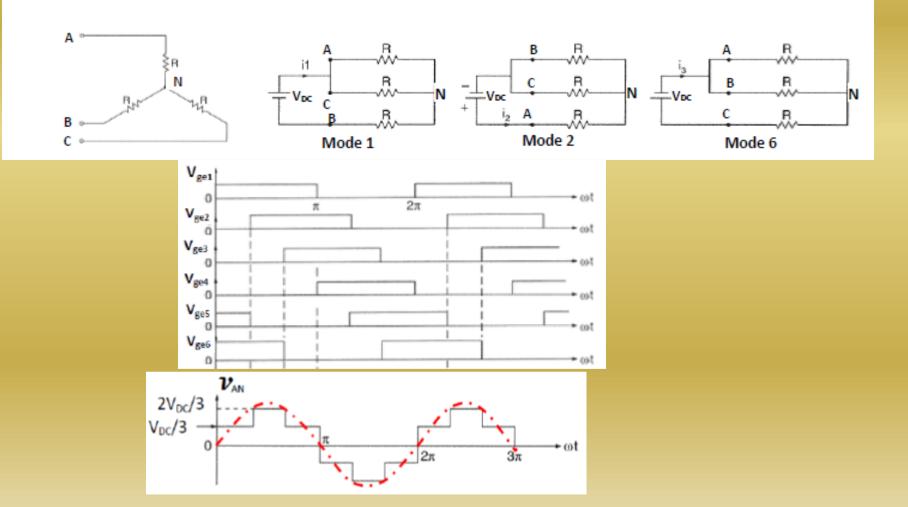

➡ The voltage waveforms for 180° conduction in each switch for a Square Wave Operation are shown in the Figure below.

The gate-emitter voltages of the switches are phase shifted by  $\frac{\pi}{3}$  (or 60°) for any two consequent switches.

- The gate-emitter voltages of the switches are phase shifted by  $\frac{\pi}{3}$  (or 60°) for any two consequent switches.

- In the same leg, the gate signals of the switches are complements of each other (180° out of phase).

- In the same inverter level, upper or lower, the gate signals of the switches are shifted by  $\frac{2\pi}{3}$  (or 120°) for consequent switches in the sequence 1-3-5-1..., or in the sequence 2-4-6-2...

The harmonic components' amplitude of the line-to-line voltage is obtained by Fourier Analysis as:

$$\hat{V}_{LLh} = \frac{4}{h\pi} V_{DC} \sin h(90 - \frac{\alpha}{2})$$

where  $\alpha$ , in this case, is  $60^{\circ}$

➡ The fundamental component's amplitude of the line-to-line voltage is:

$$\hat{V}_{LL1} = \frac{4}{(1)\pi} V_{DC} \sin(1) \left(90 - \frac{60}{2}\right)$$

$$\implies \hat{V}_{LL1} = \frac{4}{\pi} V_{DC} \sin (60)$$

$$\hat{V}_{LL1} = \frac{4}{\pi} V_{DC} \frac{\sqrt{3}}{2}$$

which can be rewritten as:

$$\hat{V}_{LL1} = \sqrt{3} \left( \frac{4}{\pi} \, \frac{V_{DC}}{2} \right)$$

i.e. the peak of the line-to-line voltage is  $\sqrt{3}$  times the peak of the phase voltage!

$$\therefore \widehat{V}_{LL1} = 1.103 V_{DC}$$

The rms value of the line-to-line voltage is then:

$$V_{LL1} = 0.78 V_{DC}$$

- Note that the line-to-line voltage leads the respective phase voltage by  $\frac{\pi}{6}$  (or 30°).

- Clearly, balanced three-phase voltages result!

The Line to Neutral voltage can be derived for a Y-connected resistive load, by deriving the equivalent circuit during each switching mode, which is 60°. Mode 1 represents the period:  $0^{\circ} < \omega t < 60^{\circ}$ , Mode 2 represents the period:  $60^{\circ} < \omega t < 120^{\circ}$ , whilst Mode 6 represents the period:  $300^{\circ} < \omega t < 360^{\circ}$ . The equivalent circuits during these modes are shown in the Figure below. Other modes for other periods can be derived.

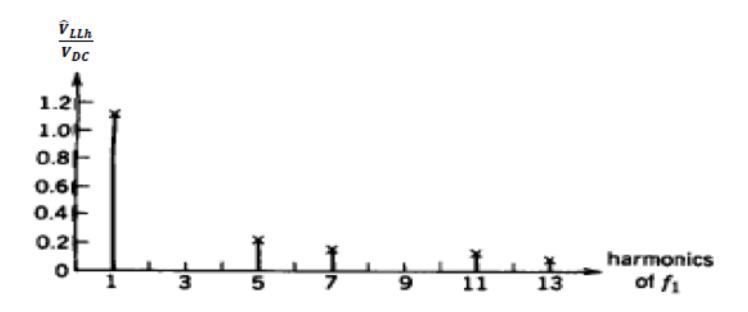

## Harmonics in the Output of a Three-Phase VSI with Square Wave Operation

The harmonics in the line-to-line voltage have amplitudes represented by the following formula:

$$\hat{V}_{LLh} = \frac{\sqrt{3}}{h} \left( \frac{4}{\pi} \, \frac{V_{DC}}{2} \right)$$

The harmonics die as  $\frac{1}{h}$ , where  $h = 6m \mp 1$ ; such that m = 1, 2, 3, 4, ...

The Frequency Spectrum of the line-to-line voltages output of a three-phase VSI in a Square Wave Mode is:

For a three-Phase VSI in a Square Wave Mode, it is not possible to control the output voltage magnitude by voltage cancellation via the inverter, as  $\alpha$  is fixed here to be 60°.

#### **General Comments:**

- The use of Half, Full, or Three-Phase Bridges to generate an AC in the 'Square Wave' Mode is simple, but the harmonic content of the output is high.

- For some applications at high frequencies, > 20kHz, such as switch mode power supplies, and radio frequency heating, the square wave is acceptable or the load can be tuned to minimize the harmonic currents.

- For AC Motor Drives, operating at around 50Hz, filtering components are very bulky and expensive.

In addition, harmonic currents may cause torque pulsation and vibrations, and severe losses and require derating of the machine. In these systems, Pulse Width Modulation (PWM) schemes are adopted to produce an output which is more closely sinusoidal.

# 2) Sinusoidal Pulse Width Modulation in Voltage Source Inverters

#### (Switch Mode DC to AC Sinusoidal AC Inverters)

Many applications, notably AC Motor Drives, require an AC source, which has a lower harmonic content than that can be obtained by a simple Square Wave operation of the inverter. An effective solution is to use Sinusoidal Pulse Width Modulation (SPWM).

It was shown earlier that the average output voltage of a Full Bridge can be made proportional to a control voltage ( $v_c$ ). The control voltage can be made sinusoidal to produce a sinusoidal output, within limits imposed by the switching frequency of the Bridge.

# 2.1) Sinusoidal Pulse Width Modulation in a Half Bridge

Consider one leg of a Full Bridge, shown in the Figure next, which is sensible for AC operation!

The transistors numbering is as before. It could be part of single-phase or three-phase Bridges.

#### **Switching Waveforms**

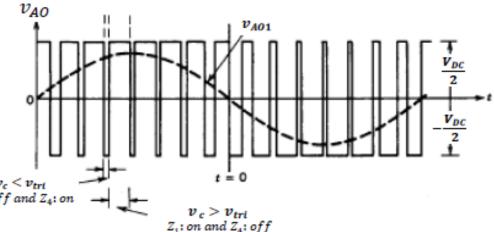

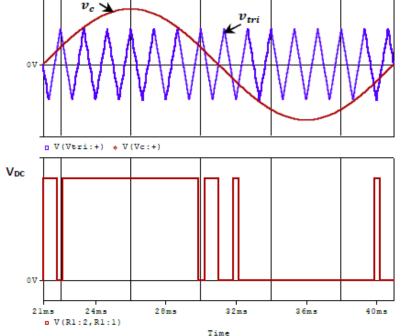

The control voltage  $(v_c)$  is sinusoidal and must be at a lower frequency than that of the triangular voltage  $(v_{tri})$ .

when  $v_c > v_{tri}$ :

$$Z_1$$

is on and  $Z_4$  is of  $f \implies v_{AO} = \frac{V_{DC}}{2}$

when  $v_c < v_{tri}$ :

$$Z_1$$

is off and  $Z_4$  is on  $\implies v_{AO} = \frac{-V_{DC}}{2}$

- The triangular signal  $(v_{tri})$  is maintained at a constant amplitude  $(\hat{V}_{tri})$ , and its frequency  $(f_s)$  is called the switching frequency or carrier frequency.

- The control voltage  $(v_c)$  modulates the duty cycle of the switches and has a variable frequency  $(f_1)$  and a variable magnitude.

- The fundamental frequency of the inverter output is, therefore, f<sub>1</sub>.

- $\triangleright$  The inverter output will contain harmonics related to  $f_1$  and  $f_s$ .

- The Amplitude Modulation Index or Ratio (M) is defined as:

$$M = \frac{\hat{V}_c}{\hat{V}_{tri}}$$

where  $\hat{V}_c$  is the amplitude of the control voltage.

$\succ$  The Frequency Modulation Ratio  $(m_f)$  is defined as:

$$m_f = \frac{Switching\ frequency}{Modulating\ frequency} = \frac{f_s}{f_1}$$

The inverter leg is controlled according to the scheme:

when

$$v_c > v_{tri}$$

,  $Z_1$  is 'on' and  $Z_4$  is 'off'  $\Rightarrow v_{AO} = \frac{v_{DC}}{2}$

when  $v_c < v_{tri}$ ,  $Z_1$  is 'off' and  $Z_4$  is 'on'  $\Rightarrow v_{AO} = -\frac{v_{DC}}{2}$

Note that a Dead time between switches is always needed in VSI legs!!

#### For $M \leq 1$ and a Half Bridge, the following apply:

1. The output voltage is:

$$v_{AO}(t) = M \frac{v_{DC}}{2} \sin \omega_1 t + Harmonics$$

The amplitude of the fundamental component is:

$$\hat{V}_{AO_1} = M \frac{V_{DC}}{2}$$

3. The harmonics in the output are centered around (at the side bands of) the switching frequency,  $f_s$ , and its multiples, and they are related by:

$$f_h = (n m_f \mp k) f_1$$

where n and k are integers. However, for odd values of n, the harmonics exist only for even values of k, and vice versa. For example,

$$1m_f \mp even$$

:  $1m_f \mp 0$ ,  $1m_f \mp 2$ ,  $1m_f \mp 4$ ,  $1m_f \mp 6$ ,  $1m_f \mp 8$ , ...

$$2m_f \mp odd: 2m_f \mp 1, 2m_f \mp 3, 2m_f \mp 5, 2m_f \mp 7, ...$$

- **4.** Adopting an odd integer for  $m_f$  in a Half Bridge results in only odd harmonics of  $m_f$  in the Frequency Spectrum (a result from signal analysis by Fourier). Note that the Frequency Modulation Ratio  $(m_f)$  for the previous waveforms is 15.

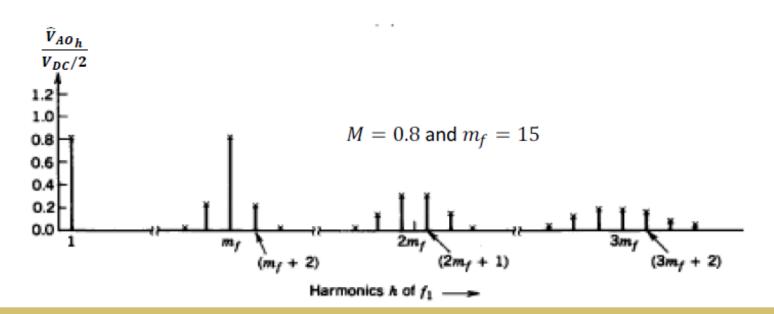

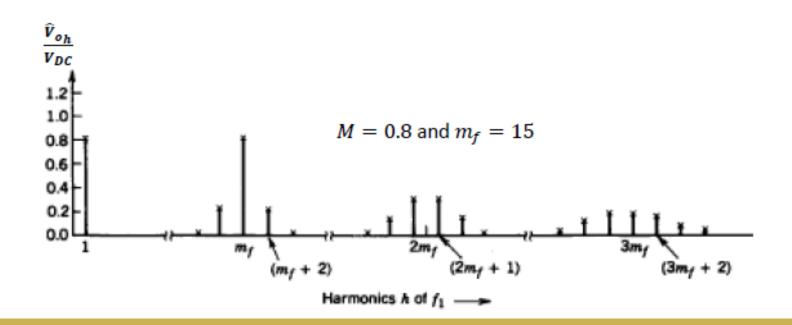

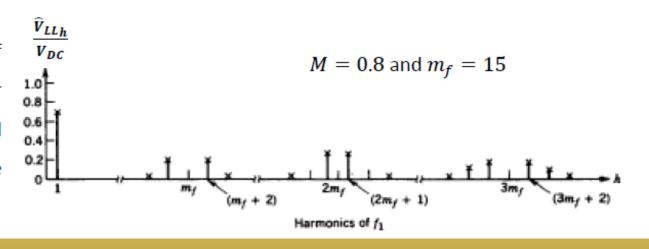

- 5. The Frequency Spectrum of the previous output voltage at  $M=0.8\ and\ m_f=15$  is shown in the Figure below. Note that there is no harmonic component at  $2m_f$ , because  $m_f$  was selected to have an odd value.

6. The amplitudes of the fundamental component and harmonics are obtained from tables. An example of these tables is shown below, which depicts the values of the fundamental component and the harmonics at the output of Half and Full Bridges for  $m_f \ge 9$ .

| M            | 0.2   | 0.4   | 0.6   | 4.0   |       |

|--------------|-------|-------|-------|-------|-------|

| <u>h</u>     | 0.2   | 0.4   | 0.6   | 0.8   | 1.0   |

| 1            | 0.2   | 0.4   | 0.6   | 0.8   | 1.0   |

| Fundamental  |       |       |       |       |       |

| $m_f$        | 1.242 | 1.15  | 1.006 | 0.818 | 0.601 |

| $m_f \pm 2$  | 0.016 | 0.061 | 0.131 | 0.220 | 0.318 |

| $m_f \pm 4$  |       |       |       |       | 0.018 |

| $2m_f \pm 1$ | 0.190 | 0.326 | 0.370 | 0.314 | 0.181 |

| $2m_f \pm 3$ |       | 0.024 | 0.071 | 0.139 | 0.212 |

| $2m_f \pm 5$ |       |       |       | 0.013 | 0.033 |

| $3m_f$       | 0.335 | 0.123 | 0.083 | 0.171 | 0.113 |

| $3m_f \pm 2$ | 0.044 | 0.139 | 0.203 | 0.176 | 0.062 |

| $3m_f \pm 4$ |       | 0.012 | 0.047 | 0.104 | 0.157 |

| $3m_f \pm 6$ |       |       |       | 0.016 | 0.044 |

| $4m_f \pm 1$ | 0.163 | 0.157 | 0.008 | 0.105 | 0.068 |

| $4m_e \pm 3$ | 0.012 | 0.070 | 0.132 | 0.115 | 0.009 |

| $4m_f \pm 5$ |       |       | 0.034 | 0.084 | 0.119 |

| $4m_f \pm 7$ |       |       |       | 0.017 | 0.050 |

# Factors Influencing the Choice of the Switching Frequency:

In general, a higher switching frequency makes the filtering of harmonics easier, but increases the switching losses in the inverter. Besides, it is very advantageous to have the switching frequency above 20kHz so that it is inaudible; i.e. audible converter noise against higher switching losses.

A second, more subtle, choice is the adoption of an odd integer for  $m_f$ , in a Half-Bridge, so that there is both odd symmetry and half wave symmetry. As a result, cosines and even harmonics disappear from the Fourier series.

# I) Small $m_f$ ( $m_f \leq 21$ )

In some machine applications, a need for an output frequency up to 200Hz and a switching frequency say 2kHz result in a low  $m_f$ . The modulating frequency  $(f_1)$  and the switching frequency  $(f_s)$  should be synchronized  $(m_f)$  should be integer) to avoid beating and appearance of subharmonics. Beating may occur if  $f_s$  is close to  $f_1$  (the harmonics may be amplified depending on the output filter characteristics), which is a problem in Thyristor inverters.

# II) Large $m_f$ ( $m_f > 21$ )

Synchronization of  $f_s$  and  $f_1$  is not so important, as the amplitudes of the beat frequency components are less. Nevertheless, synchronization is advisable with inverters supplying AC machines. However, synchronization is preferable; select  $m_f$  to be an integer always!

## Over Modulation (M > 1)

For  $M \leq 1$ , the amplitude of the fundamental component at the output is proportional to the amplitude of the control voltage, and the harmonics are pushed up to around the switching frequency.

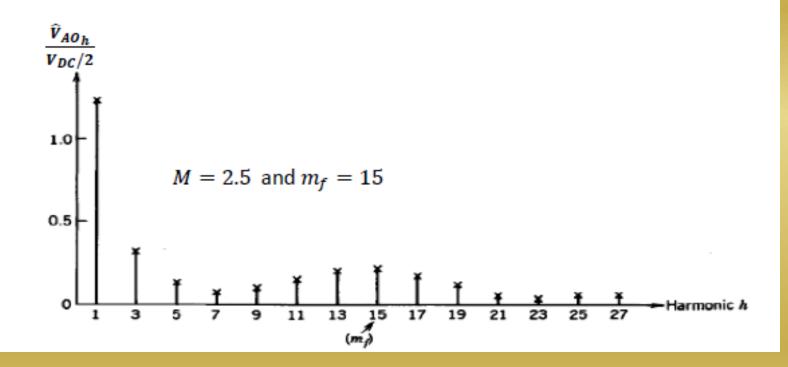

However, a greater output can be obtained at the cost of increased harmonic content by making M > 1. Ultimately, a Square Wave Mode results!

The relation between the output voltage and a wide range of Modulation Index is illustrated in the Figure next. There are three distinctive regions: a Linear region ( $M \le 1$ ), an Over Modulation region (1 < M < 3.24), and a Square Wave region (M > 3.24).

There are trade-offs; a Square Wave mode gives a higher output, but more harmonics.

The Frequency Spectrum of the output at  $M=2.5\ and\ m_f=15$  is shown in the Figure below.

### 2.2) Sinusoidal Pulse Width Modulation in a Single-Phase Voltage Source Inverter

The Sinusoidal Pulse Width Modulation (SPWM) scheme can be realized in a Full bridge using either Bipolar or Unipolar Switching Strategies.

#### 2.2.1) Bipolar Switching Strategy

As illustrated before, a Bipolar switching strategy treats every two switches as a pair;  $Z_1\&Z_2$  is a pair, and  $Z_3\&Z_4$  is the second pair. The switches in each pair are switched together, simultaneously.

Therefore, one control voltage  $(v_c)$  is compared with a triangular signal  $(v_{tri})$  to produce the gate signals of the switches pairs, which are complement to each other.

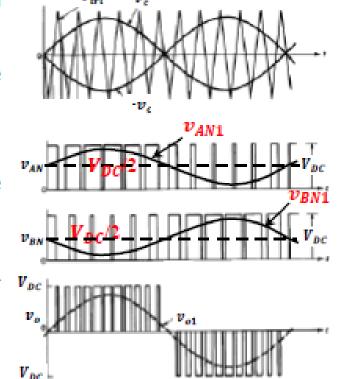

$v_{AN}\ and\ v_{BN}$  are the voltages at the midpoints of Leg A and Leg B with respect to the negative terminal of the supply, respectively.

The output of each leg with respect to  $\frac{v_{DC}}{2}$  is the

same as that of a Half Bridge, but they are shifted from each other by 180°.

For Bipolar switching, the output is given by:

$$v_o = v_{AN} - v_{BN}$$

The output voltage for  $M \leq 1$  is:

$$v_o(t) = M \frac{v_{DC}}{2} \sin \omega_1 t - M \frac{v_{DC}}{2} \sin(\omega_1 t - 180^o) + Harmonics$$

$$v_o(t) = M \frac{v_{DC}}{2} \sin \omega_1 t + M \frac{v_{DC}}{2} \sin \omega_1 t + Harmonics$$

$$v_o(t) = 2M \frac{v_{DC}}{2} \sin \omega_1 t + Harmonics$$

The dotted/dashed curves represent the fundamental component for the respective voltage.

$v_o(t) = MV_{DC} \sin \omega_1 t + Harmonics$

The harmonics in the output are similar to those found in the output of one leg. The harmonics are, also, centered around (at the side bands of) the switching frequency, f<sub>s</sub>, and its multiples, and they are related by:

$$f_h = (n m_f \mp k) f_1$$

where n and k are integers. However, for odd values of n, the harmonics exist only for even values of k, and vice versa.

$ightharpoonup m_f$  is selected to be odd for Bipolar Switching Strategy in a Full Bridge.

The Frequency Spectrum of the output voltage, for example, at M=0.8 and  $m_f=15$  is shown in the Figure below.

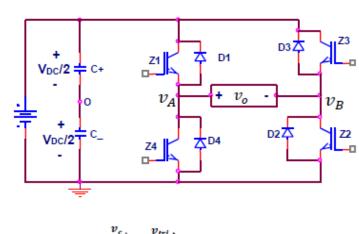

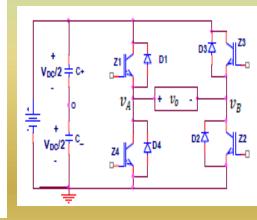

# 2.2.2) Unipolar Switching Strategy

It was noted earlier, in the DC-DC Converter, that the Unipolar switching doubles the effective switching frequency at the output without increasing the switching losses in the inverter. It is also an attractive feature in single phase inverters.

- Each inverter Leg is controlled by its own control voltage, independent from the other. Hence, two control voltages (v<sub>c</sub> and -v<sub>c</sub>) are needed.

- The control voltages are sinusoidals, and have the same magnitude, but they are 180° out of phase.

- v<sub>c</sub> controls the switches in Leg A, whilst -v<sub>c</sub> controls the switches in Leg B.

- The control voltages are compared with the same triangular voltage (v<sub>tri</sub>).

The Unipolar strategy is implemented according to the following:

- when  $v_c>v_{tri}\implies Z_1$  is turned 'on' and  $Z_4$  is turned 'off' Leg's A voltage with respect to the supply negative terminal is  $v_{AN}=V_{DC}$

- when  $v_c < v_{tri} \implies Z_1$  is turned 'off' and  $Z_4$  is turned 'on' Leg's A voltage with respect to the supply negative terminal is  $v_{AN}=0$

- when  $-v_c>v_{tri}\Longrightarrow Z_3$  is turned 'on' and  $Z_2$  is turned 'off' Leg's B voltage with respect to the supply negative terminal is  $v_{BN}=V_{DC}$

- when  $-v_c < v_{tri} \implies Z_3$  is turned 'off' and  $Z_2$  is turned 'on'

Leg's B voltage with respect to the supply negative terminal is  $v_{BN}=0$

The output voltage is:

$$v_o = v_{AN} - v_{BN}$$

For  $M \le 1$ , the output voltage, again, is:

$$v_o(t) = MV_{DC} \sin \omega_1 t + Harmonics$$

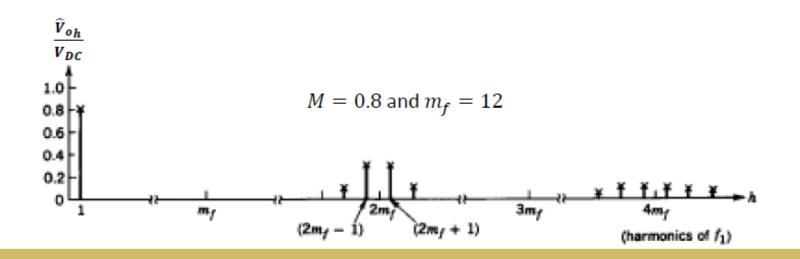

The effective doubling of the switching frequency at the output in the Unipolar scheme shifts the harmonics up in frequency. The harmonics have frequencies represented by the following equation:

$$f_h = (n \ 2m_f \mp k) f_1$$

where n and k are again integers. But, since the coefficient of  $m_f$  is "2n", which is always even, k takes odd values only!

Tompared with the Bipolar strategy, filtering is easier with Unipolar, as harmonics are at higher frequencies for the same inverter switching losses.

- $m_f$  is selected to be an even integer for Unipolar Switching Strategy, to eliminate particular harmonics off the spectrum. The phase difference between harmonics in  $v_{AN}$  and  $v_{BN}$  is  $180^o m_f$ , so if  $m_f$  was selected to be even, some of these harmonics would be in phase and would cancel each other.

- The Frequency Spectrum of the output voltage, for example, at  $M=0.8~and~m_f=12$  is shown in the Figure below.

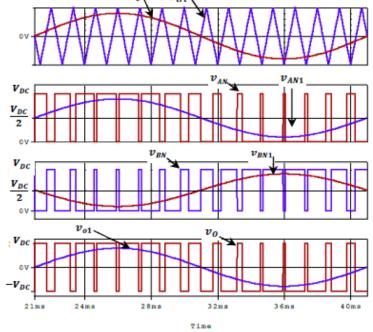

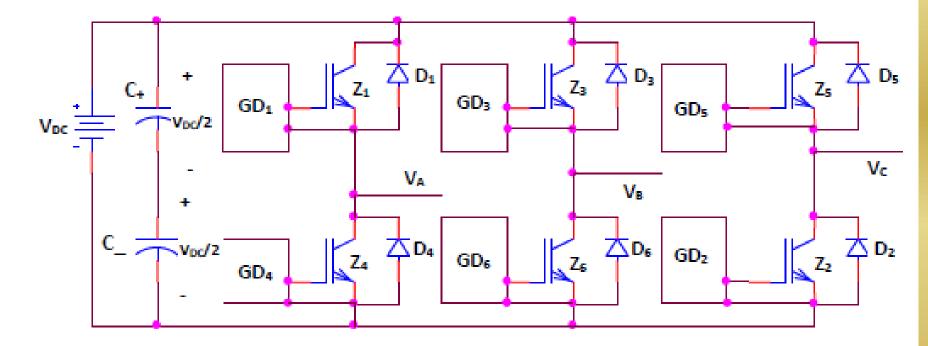

# 2.3) Sinusoidal Pulse Width Modulation in a Three-Phase Voltage Source Inverter

The three-phase Bridge (Inverter) can also be used with Sinusoidal Pulse Width Modulation (SPWM).

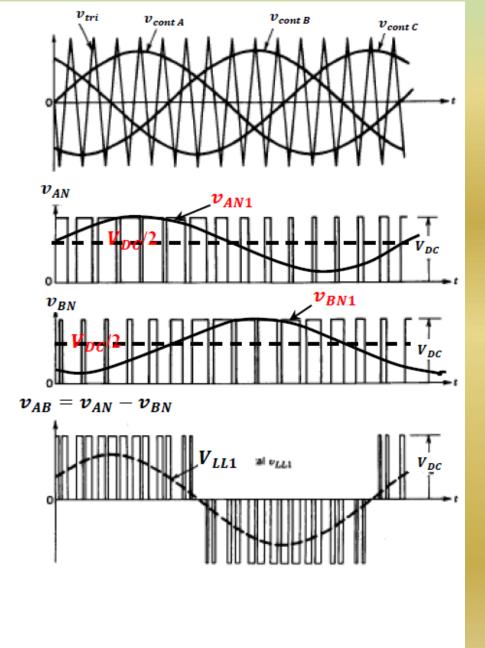

- Three control voltages (v<sub>cont A</sub>, v<sub>cont B</sub>, and v<sub>cont C</sub>), which are 120° out of phase from each other, are compared with a common triangular voltage (v<sub>tri</sub>) to produce the gate signals for each switch (IGBT) in the respective leg.

- SPWM generation can be achieved either by:

- Microcontroller/Microprocessors

- Chips; for example MA828

- The control strategy is implemented according to the following:

- when  $v_{cont\,A} > v_{tri} \implies Z_1$  is turned 'on' and  $Z_4$  is turned 'off'

Leg's A voltage with respect to the supply negative terminal is  $v_{AN} = V_{DC}$

ullet when  $v_{cont\,A} < v_{tri} \implies Z_1$  is turned 'off' and  $Z_4$  is turned 'on'

Leg's A voltage with respect to the supply negative terminal is  $\emph{v}_{AN}=0$

• when  $v_{cont\,B} > v_{tri} \Longrightarrow Z_3$  is turned 'on' and  $Z_6$  is turned 'off'

Leg's B voltage with respect to the supply negative terminal is  $v_{\mathit{BN}} = V_{\mathit{DC}}$

ullet when  $v_{cont\,B} < v_{tri} \implies Z_3$  is turned 'off' and  $Z_6$  is turned 'on'

Leg's B voltage with respect to the supply negative terminal is  $\,v_{{\scriptscriptstyle BN}}=0\,$

ullet when  $v_{cont\ C}>v_{tri}\Longrightarrow\ Z_5$  is turned 'on' and  $Z_2$  is turned 'off'

Leg's C voltage with respect to the supply negative terminal is  $v_{\it CN} = V_{\it DC}$

ullet when  $v_{cont\ C} < v_{tri} \implies Z_5$  is turned 'off' and  $Z_2$  is turned 'on'

Leg's C voltage with respect to the supply negative terminal is  $v_{\it CN}=0$

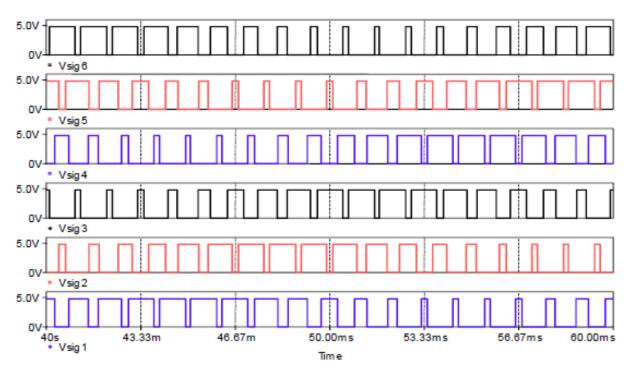

The switching waveforms are shown in the Figure next.

- Note that the fundamental line-to-line voltage  $(v_{AB_1})$  leads  $v_{AN_1}$  by 30°, which is consistent with three-phase concept.

- For 0 ≤ M ≤ 1, the fundamental component of one leg, for example Leg A, has an amplitude of:

$$\widehat{V}_{AN_1} = M \frac{V_{DC}}{2}$$

Thus, the amplitude of the fundamental component of the line-to-line voltage is:

$$\hat{V}_{LL_1} = \sqrt{3} M \frac{V_{DC}}{2}$$

$$\Rightarrow \hat{V}_{LL_1} = 0.866 M V_{DC}$$

The rms value of the line-to-line voltage is:

$$V_{LL_{1rms}} = \frac{\sqrt{3}}{\sqrt{2}} M \frac{V_{DC}}{2}$$

$$V_{LL_{1rms}} = 0.612MV_{DC}$$

Therefore, the output line-to-line voltage between phases 'A' and 'B' is:

$$v_{AB}(t) = \mathbf{0.866} M V_{DC} \sin(\omega_1 t + \frac{\pi}{6}) + Harmonics$$

- The comments for Over Modulation apply also for three-phase inverters.

- The harmonic content of line-to-line voltage can be reduced by making  $m_f$  odd and multiple of 3. This suppresses harmonics at  $m_f$  and  $3nm_f$ , where n is an integer. Because some of the harmonics in the phase voltages are phase shifted from each other by  $120^o m_f$ . Consequently, eliminating each other from the line-to-line voltages.

The Frequency Spectrum of the line-to-line voltage, for example, at M=0.8 and  $m_f=15$  is shown in the Figure next.

# Space Vector Modulation (SVM)

### Introduction

- The SVM is a method of generating a sequence of switching combinations of the inverter. Each combination is called a state.

- The Space Vector (SV) is a complex number that can be represented by any three quantities, not necessarily sinusoidal, which add up to zero (with the neutral being disconnected).

- These states can be represented in the complex plane by Space Vectors (SVs) and are of two types; zero and non-zero states.

- In a Current Source Inverter (CSI), a non-zero state allows the DC link current (I<sub>dc</sub>) to complete its path through the output load, whilst a zero state shorts one of the inverter legs and no current, from the DC bus, passes to the load (I<sub>dc</sub> completes its path through one of the inverter legs). In a CSI, there are six non-zero and three zero states.

- In a Voltage Source Inverter (VSI), during non zero states the DC link voltage is applied to the load, whilst no voltage is applied to the load during the zero states. Thus, in a VSI there are six non-zero and two zero states only.

- Therefore, more switching sequences are available in a CSI, because of the increased degrees of freedom in choosing the zero state.

# Advantages of SVM over other PWM Techniques:

- 1. It is easier and more feasible for digital implementations and microprocessor control.

- It reduces the switching frequency of the inverter. For example, compared with an equivalent Sinusoidal PWM based system, the switching frequency will be reduced to approximately half the carrier frequency.

- 3. A Modulation Index of 1.15 can be reached without any constraints. On the other hand, for Sinusoidal PWM, in the case of over-modulation, some pulses are dropped and low order harmonics appear at the output, which can be avoided by the addition of Triplen harmonic to the sinusoidal modulating waveforms.

- 4. The AC Gain is higher in SVM. For a three-phase Inverter, the AC Gain is defined as:

$$G_{AC} = \frac{\widehat{v}_{LL1}}{v_{DC}}\Big|_{M=1}$$

The AC Gain for SVM is 1, whilst it is 0.866 for SPWM.

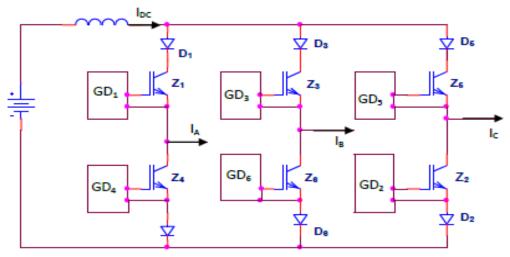

### Space Vector Modulation (SVM) in a Current Source Inverter

- The Space Vector (SV) is a complex number that can be represented by any three quantities, not necessarily sinusoidal, which add up to zero (with the neutral being disconnected).

- The topology of a Current Source Inverter (CSI) is shown in the Figure below.

The Space Vector Current (In) associated with the AC line currents of a three-phase CSI can be generated by a proper selection of the SVs that represent the states. In is given by:

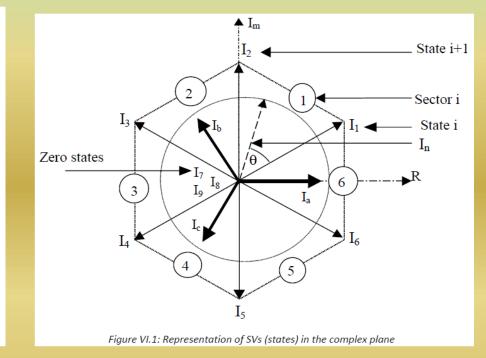

$$I_{n} = \frac{2}{3} \left( i_{a} + i_{b} * e^{j\frac{2\pi}{3}} + i_{c} * e^{-j\frac{2\pi}{3}} \right) = R + jI_{m}$$

(VI.1)

where  $i_a$ ,  $i_b$ , and  $i_c$  are the instantaneous magnitudes of the three-phase line currents, refer to Figure VI.1, R and  $I_m$  are the real and the imaginary components of  $I_n$ , respectively.

Each state produces three-phase line currents, the magnitude of each is defined in Table VI.1. The table shows the nine-possible states for a CSI with the associated 'ON' switches, while the other switches are 'OFF', and the respective per unit line currents, with the DC link current (I<sub>dc</sub>) chosen as the base quantity.

Table VI.1: Possible states and their respective per-unit line currents in a CSI.

| State          | 'ON' switches                   | i <sub>a</sub> / I <sub>dc</sub> | i <sub>b</sub> / I <sub>dc</sub> | i <sub>c</sub> / I <sub>dc</sub> |

|----------------|---------------------------------|----------------------------------|----------------------------------|----------------------------------|

| l <sub>1</sub> | S <sub>1</sub> , S <sub>2</sub> | 1                                | 0                                | -1                               |

| l <sub>2</sub> | S <sub>2</sub> , S <sub>3</sub> | 0                                | 1                                | -1                               |

| I <sub>3</sub> | S <sub>3</sub> , S <sub>4</sub> | -1                               | 1                                | 0                                |

| I <sub>4</sub> | S <sub>4</sub> , S <sub>5</sub> | -1                               | 0                                | 1                                |

| I <sub>5</sub> | S <sub>5</sub> , S <sub>6</sub> | 0                                | -1                               | 1                                |

| I <sub>6</sub> | S <sub>6</sub> , S <sub>1</sub> | 1                                | -1                               | 0                                |

| l <sub>7</sub> | S <sub>1</sub> , S <sub>4</sub> | 0                                | 0                                | 0                                |

| I <sub>8</sub> | S <sub>3</sub> , S <sub>6</sub> | 0                                | 0                                | 0                                |

| l <sub>9</sub> | S <sub>5</sub> , S <sub>2</sub> | 0                                | 0                                | 0                                |

Figure VI.1 shows the SVs representing the states, the line currents, and  $I_n$  in the complex plane.  $I_n$  is represented by an equivalent SV, having a magnitude and an angular position  $\theta$  depending on the state SVs representing it. The objective of SVM technique is to approximate  $I_n$  with the nine SVs ( $I_k$ , k=1...9) available in the CSI. So that it will have an amplitude proportional to the Modulation Index (M), and rotating in the complex plane with an angular velocity ( $\omega$ ) proportional to the frequency of the fundamental output current ( $I_n$ ). By approximating  $I_n$  using the nearest two non-zero SVs, ( $I_n$  and  $I_{n+1}$ ), and one zero SV, ( $I_n$  =  $I_n$ ,  $I_n$  or  $I_n$ ), the AC Gain of the technique is maximized and the switching frequency is minimized, as seen in Table VI.2.

The AC Gain ( $G_{AC}$ ) is defined as the maximum value of the fundamental component of the line-to-line voltage to the amplitude of the unfiltered pulses compromising the same component (the DC value).

Thus, if the Space Vector Current  $(I_n)$  is lying between the arbitrary space vectors  $I_i$  and  $I_{i+1}$ , the following expressions can be derived:

$$I_n * t_{cycle} = I_i * t_i + I_{i+1} * t_{i+1} + I_z * t_z$$

(VI.2)

where  $t_{cycle}$  is the period of one carrier cycle ( $t_{cycle} = 1/f_c$ ), while  $t_i$ ,  $t_{i+1}$ , and  $t_z$  are the times of state i, i+1 and zero-state (for M  $\leq$  1), respectively. Their values can be calculated using the following equations:

$$t_i = t_{cycle} * M * sin ((\pi/3)-\theta)$$

(VI.3)

$$t_{i+1} = t_{cycle} * M* sin(\theta)$$

(VI.4)

$$t_z = t_{cycle} - t_i - t_{i+1}$$

(VI.5)

$$\theta = \omega_1 * t \tag{VI.6}$$

$$\omega_1 = 2 * \pi * f_1$$

(VI.7)

Such that  $f_1=1/T$ , is the fundamental frequency at the output

The Space Vector Current (In) can be moved in the complex plane by a step of:

$$\Delta\theta = \frac{360f_1}{f_c} \tag{VI.8}$$

## Selection of States

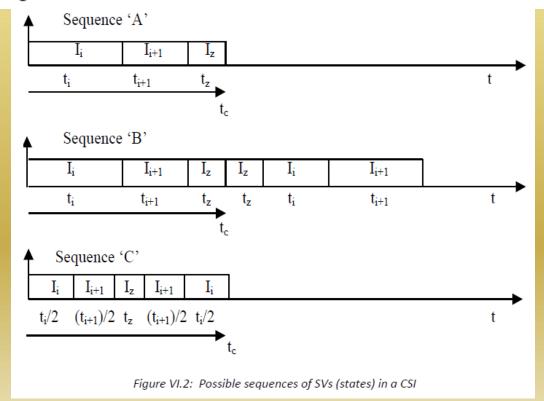

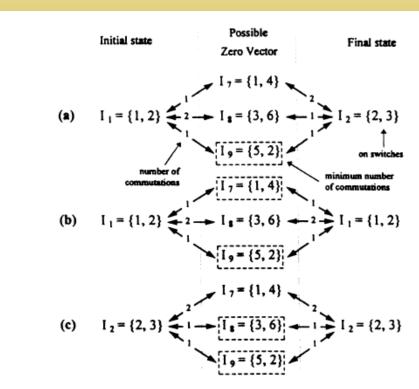

Within one sector, only three states are used to represent  $I_n$ . However, the sequence in which the states are used to control the inverter switches can be designed. Some of these sequences are known as Sequence 'A', Sequence 'B', and Sequence 'C', and are shown in Figure VI.2. Once the SV sequence is fixed, the selection of the zero SV defines the switching frequency, but the line current wave-shape does not depend upon the selected zero SV. Figure VI.3 shows the possible state transitions between states  $I_1$  to  $I_2$  in sector 1. Table VI.3 shows the zero SV ( $I_2$ ) to be used in each sector in order to minimise the switching frequency, and hence the switching losses.

Table VI.2: The switching sequence dictates the switching frequency and the AC Gain

| Technique                | Category | Switching frequency (f <sub>sw</sub> ) | AC Gain (GAC) |

|--------------------------|----------|----------------------------------------|---------------|

| Sinusoidal PWM           | Analogue | $\mathbf{f}_{c}$                       | 0.866         |

| Third Harmonic Injection | Analogue | fc                                     | 1             |

| Trapezoidal PWM          | Analogue | fc                                     | 1.053         |

| Dead-band PWM            | Analogue | 2/3*fc-1                               | 1             |

| Mod. Dead-band           | Analogue | ½*(f <sub>c</sub> +1)                  | 1             |

| SVM, Seq.'A'             | Digital  | f <sub>c</sub> /2                      | 1             |

| SVM, Seq.'B'             | Digital  | 5*(f <sub>c</sub> /12)-1               | 1             |

| SVM, Seq.'C'             | Digital  | (f <sub>c</sub> /2)-1                  | 1             |

(a) Transition: I1 to I2 to I2 OR I2 to I2 to I1

(b) Transition: I2 to I2 to I1

(c) Transition: I2 to Iz to I2

Table VI.3: Sectors and respective zero states recommended for minimum switching frequency in a CSI.

| Sectori | li             | l <sub>i+1</sub> | Iz             |

|---------|----------------|------------------|----------------|

| 1       | l <sub>1</sub> | l <sub>2</sub>   | l <sub>9</sub> |

| 2       | I <sub>2</sub> | l <sub>3</sub>   | I <sub>8</sub> |

| 3       | I <sub>3</sub> | l <sub>4</sub>   | I <sub>7</sub> |

| 4       | l <sub>4</sub> | l <sub>5</sub>   | l <sub>9</sub> |

| 5       | I <sub>5</sub> | I <sub>6</sub>   | I <sub>8</sub> |

| 6       | I <sub>6</sub> | l <sub>1</sub>   | I <sub>7</sub> |

Figure VI.3: Possible state transitions in sector 1 involving a zero SV for a CSI

#### SVM and Sinusoidal PWM Waveforms in a CSI

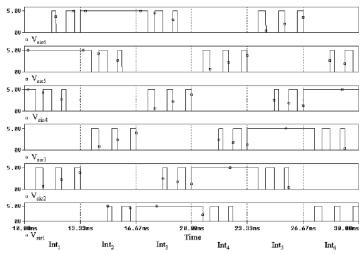

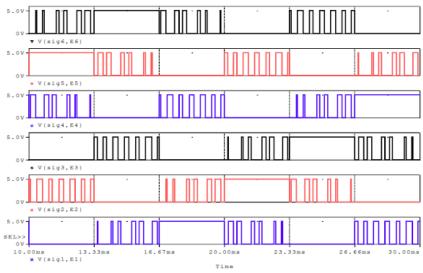

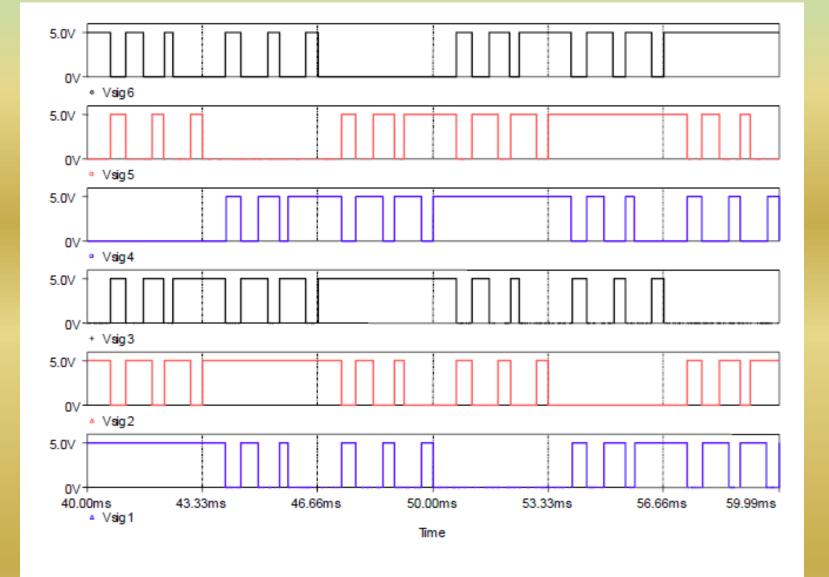

For M=0.7 and  $f_c=900$ Hz, the gate signals obtained by SVM for a VSI are shown in Figure VI.4. On the other hand, Figure VI.5 shows the comparative sinusoidal PWM gate signals. It is clear that the number of switching transitions is minimized.

Figure VI.4: The SVM signals in a CSI for M = 0.7 and  $f_c = 900$ Hz

Figure VI.5: The equivalent Sinusoidal PWM signals in a CSI for M = 0.7 and  $f_c = 900$ Hz

Clearly, the switching frequency has been reduced for a similar harmonic content.

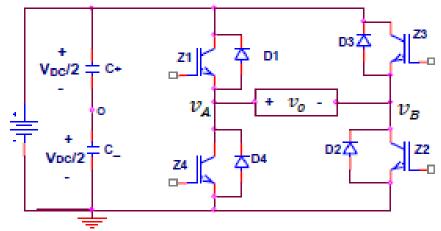

# Space Vector Modulation in a Voltage Source Inverter

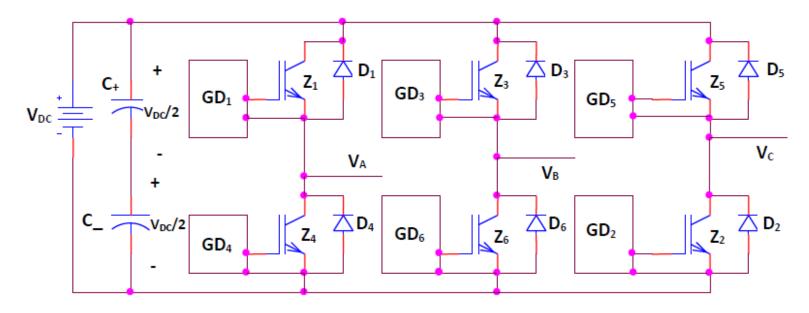

The topology of a three-phase Voltage Source Inverter (VSI) is shown in the Figure below.

- The Space Vector (SV) is a complex number that can be represented by any three quantities, not necessarily sinusoidal, which add up to zero.

- The Space Vector Voltage (V<sub>n</sub>) associated with the AC phase voltages of a three-phase VSI can be generated by a proper selection of the SVs that represent the states. V<sub>n</sub> is given by:

$$V_{n} = \frac{2}{3} \left( V_{a} + V_{b} * e^{j\frac{2\pi}{3}} + V_{c} * e^{-j\frac{2\pi}{3}} \right) = R + jI_{m}$$

(VI.1')

where  $v_a$ ,  $v_b$ , and  $v_c$  are the instantaneous magnitudes of the three-phase line voltages, refer to Figure VI.6, R and  $I_m$  are the real and the imaginary components of  $V_n$ , respectively.

- There are 8 states in the VSI: 6 non-zero states and 2 zero states. The space vectors are shown in Figure VI.6. Each state produces three phase voltages as seen in Table VI.4.

- ◆ Assuming that the Space Vector Voltage (V<sub>n</sub>) is lying between the arbitrary space vectors V<sub>i</sub> and V<sub>i+1</sub>, the following expressions can be derived:

$$V_n * t_{cycle} = V_i * t_i + V_{i+1} * t_{i+1} + V_z * t_z$$

(VI.2')

where  $t_{cycle}$  is the period of one carrier cycle ( $t_{cycle} = 1/f_c$ ), whilst  $t_i$ ,  $t_{i+1}$ , and  $t_z$  are the times of state i, i+1 and zero-state (for  $M \le 1$ ), respectively. Their values can be calculated using the following equations:

$$t_i = t_{cycle} * M * sin ((\pi/3)-\theta)$$

(VI.3')

$$t_{i+1} = t_{cycle} * M* sin(\theta)$$

(VI.4')

$$t_z = t_{cycle} - t_i - t_{i+1} \tag{VI.5'}$$

$$\theta = \omega_1 * t \tag{VI.6'}$$

$$\omega_1 = 2 * \pi * f_1$$

(VI.7')

Such that  $f_1 = 1/T$ , is the fundamental frequency of the output

The Space Vector Voltage (V<sub>n</sub>) moves in the complex plane by a step of:

$$\Delta\theta = \frac{^{360}f_1}{f_c} \tag{VI.8'}$$

Table VI.4: Possible states and their respective per unit voltages

| State          | 'ON' switches                                    | va/ V <sub>dc</sub> | v <sub>b</sub> / V <sub>dc</sub> | v <sub>c</sub> / V <sub>dc</sub> |

|----------------|--------------------------------------------------|---------------------|----------------------------------|----------------------------------|

| V <sub>1</sub> | S <sub>1</sub> , S <sub>6</sub> , S <sub>2</sub> | 1                   | 0                                | 0                                |

| V <sub>2</sub> | S <sub>1</sub> , S <sub>3</sub> , S <sub>2</sub> | 1                   | 1                                | 0                                |

| V <sub>3</sub> | S4, S3, S2                                       | 0                   | 1                                | 0                                |

| V <sub>4</sub> | S4, S3, S5                                       | 0                   | 1                                | 1                                |

| V <sub>5</sub> | S4, S6, S5                                       | 0                   | 0                                | 1                                |

| V <sub>6</sub> | S <sub>1</sub> , S <sub>6</sub> , S <sub>5</sub> | 1                   | 0                                | 1                                |

| V <sub>7</sub> | S <sub>1</sub> , S <sub>3</sub> , S <sub>5</sub> | 1                   | 1                                | 1                                |

| V8             | S4, S6, S2                                       | 0                   | 0                                | 0                                |

#### Switching Sequences in a VSI

There are two main switching sequences in a VSI: Direct-Direct sequence and Direct-Inverse sequence.

#### 1. Direct-Direct Sequence

It uses V<sub>7</sub>, state 7 (111), as the zero state in sectors 1, 3 and 5, and V<sub>8</sub>, state 8 (000), as the zero state in Table VI.4: Possible states and their respective per unit voltage. sectors 2, 4 and 6. The switching sequence remains the same during the same sector; for example in the first sector, the switching sequence V<sub>1</sub>, V<sub>2</sub>, V<sub>7</sub>, V<sub>1</sub>, V<sub>2</sub>, V<sub>7</sub>, and so on... The switching frequency for this strategy is (2/3)\*f<sub>c</sub>.

#### 2. Direct-Inverse Sequence

It uses redundancy of the two zero states in the same sector to reduce the number of commutations per cycle. The switching sequence is reversed after passing through each zero state; for example in the first sector, the sequence is  $V_1$ ,  $V_2$ ,  $V_7$ ,  $V_2$ ,  $V_1$ ,  $V_8$ , and so on... The advantage of this strategy is that it gives three commutations per cycle and gives symmetrical pulses. The switching frequency for this strategy is  $(1/2)*f_c$ .

Each switching sequence has its own advantages and disadvantages in terms of switching losses and current ripple at the output. The selection of the switching sequence should be made according to the type of load, and the range of Modulation Index, etc.

| State          | 'ON' switches                                    | va/ Vdc | v <sub>b</sub> / V <sub>dc</sub> | v <sub>c</sub> / V <sub>dc</sub> |

|----------------|--------------------------------------------------|---------|----------------------------------|----------------------------------|

| V <sub>1</sub> | S <sub>1</sub> , S <sub>6</sub> , S <sub>2</sub> | 1       | 0                                | 0                                |

| V <sub>2</sub> | S <sub>1</sub> , S <sub>3</sub> , S <sub>2</sub> | 1       | 1                                | 0                                |

| V <sub>3</sub> | S4, S3, S2                                       | 0       | 1                                | 0                                |

| V <sub>4</sub> | S4, S3, S5                                       | 0       | 1                                | 1                                |

| V <sub>5</sub> | S4, S6, S5                                       | 0       | 0                                | 1                                |

| V <sub>6</sub> | S <sub>1</sub> , S <sub>6</sub> , S <sub>5</sub> | 1       | 0                                | 1                                |

| V <sub>7</sub> | S <sub>1</sub> , S <sub>3</sub> , S <sub>5</sub> | 1       | 1                                | 1                                |

| V8             | S4, S6, S2                                       | 0       | 0                                | 0                                |

### SVM and Sinusoidal PWM in a VSI

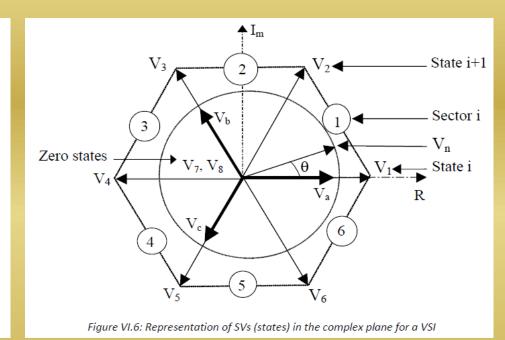

For M = 0.7 and  $f_c$  = 900Hz, the sinusoidal PWM gate signals for a VSI are shown in Figure VI.7. On the other hand, Figure VI.8 shows the comparative gate signals obtained by SVM. It is clear that the number of switching transitions is minimized.

Figure VI.7: The sinusoidal PWM gate signals for a VSI

Figure VI.8: The SVM gate signals for a VSI, Direct-Direct sequence

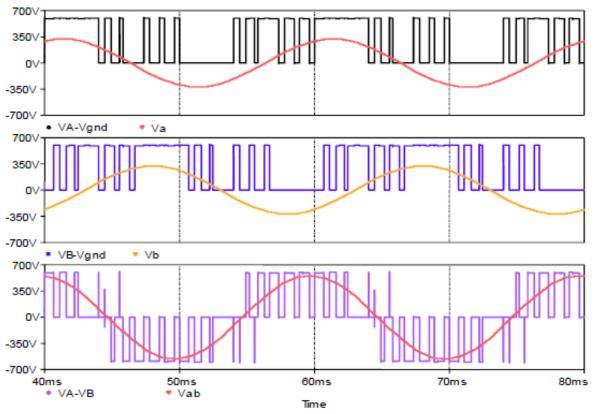

The voltage at the mid-point of the inverter is Pulse Width Modulated and has a fundamental component of 50Hz. Figure VI.9 shows the output voltages of a three phase VSI employing SVM with  $f_c$  = 900Hz and M = 0.7. Clearly there are some pulses, which are dropped from the line-to-line voltage ( $V_{AB}$ ).

Figure VI.9: The voltage waveforms in a VSI employing SVM

## Example:

Show that the Square Wave Mode (six-step) is a special case of SVM, whose  $t_{cycle} = T/6$  (such that  $f_1 = 1/T$ ) and M = 1.1547.

#### Solution:

The time for state 'i' in sector 'i' is  $t_i = t_{cycle} * M * sin ((\pi/3)-\theta)$

For  $\theta = 0$  and under the above condition:

$$t_i = T/6$$

$$t_{i+1} = t_{cycle} * M* sin(\theta)$$

and

$$t_z = t_{cycle} - t_i - t_{i+1}$$

.

Therefore,  $t_{i+1} = 0$ , and  $t_z = 0$ .

Thus, during one sixth of the period, only the switches which correspond to state vector 'i' are 'On'. Similarly, in the sector 'i+1', only the switches which correspond to the state vector 'i+1' are 'On'. Consequently, during one period (20ms), each non-zero state will be used for 3.333ms.

My Best Wishes of Success and Good Luck